The NanoIC pilot line has the ambition to become the world’s professional R&D pilot line beyond semiconductor technology.

It aims to strengthen Europe’s leadership in the global semiconductor ecosystem and support the vision of the European Chip Act to drive innovation in key markets such as computing, communications, mobility, energy and health. The NanoIC pilot line serves as an important bridge between cutting-edge research and commercial applications, playing a central role in strengthening Europe’s position at the forefront of semiconductor innovation and competitiveness.

A robust lab-to-factory conduit is essential to bridging the gap between research innovation and commercialization in the semiconductor industry. The NanoIC pilot line accelerates innovation in computing system architectures by maturing specific semiconductor technologies. The goal is to enable European companies to further lead in semiconductor innovation.

Specifically, the NanoIC pilot line provides a system-on-chip (SoC) pilot line beyond 2nm for the development and maturation of selected advanced logic, memory, and interconnect technologies. The project focuses on large-scale capacity building, collaborative R&D, maturation of advanced technologies for prototyping, and innovation support, particularly in imec’s cleanroom in Leuven (Belgium), providing access to these advanced technologies across the semiconductor ecosystem. Participants, regardless of their role in the value chain, can approach the NanoIC pilot line in the way that best suits their specific needs and innovation goals. This will enable early insight into emerging areas and help Europe remain competitive across the entire semiconductor value chain, from materials, equipment, processes and devices to designs and systems.

NanoIC Consortium

The NanoIC pilot line project consortium is led by imec, alongside France’s CEA-Leti, Germany’s Fraunhofer Gesellschaft (FhG), Finland’s VTT Technology Research Center, Ireland’s Tyndall National Laboratory, and Romania’s Bucharest University of Technology Center for Surface Science and Nanotechnology. It is supported by the Flemish government, other participating countries and the Chip Joint Venture. All partners will work together to ensure the successful implementation of the pilot line.

Building blocks of future computing systems

Nanosheet class logic devices are expected to improve scaling and performance through three additional generations (N2, A14, and A10). Complementary field-effect transistor (CFET) architectures are currently predicted to be introduced at the A7 node around 2031 and represent a major inflection point in CMOS device design. Advances in this field require extensive research into new materials, process modules, equipment, and advanced patterning capabilities, which is where high numerical aperture extreme ultraviolet (high NA EUV) lithography comes into play.

Memory innovations are focused on new magnetic memories, more specifically spin-orbit-torque magnetic random access memory (SOT-MRAM) and embedded dynamic random access memory (eDRAM). For the latter, alternative 2T0C configurations are being developed, including the exploration of wide bandgap semiconductors, such as semiconductor oxides such as indium gallium zinc oxide and 2D transition metal dichalcogenides, which have shown promise as alternative channel materials. In parallel, the development of 3D memory platforms that explore future new memory options to augment SRAM and DRAM is essential to address the memory capacity and memory bandwidth challenges posed by new workloads.

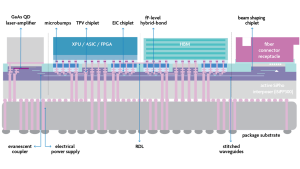

Integrating various dies into a system requires advanced electrical and optical interconnects of 2nm or greater. To further advance electrical interconnections, 3D heterogeneous integration such as die-to-wafer (D2W) hybrid bonding techniques will become possible. To electrically connect die side-by-side and enable 2.5D chiplet integration on a low-cost interposer platform, the NanoIC pilot line targets sub-2µm lines and offers fine-pitch redistribution layer (FP RDL) technology based on copper lines and vias embedded in polymer.

The aforementioned cutting-edge logic, memory, and interconnect technologies defined in industry-relevant dimensions are at the heart of the NanoIC pilot line. Achieving them requires the evaluation of new processes and materials, requires tighter process controls, and relies on a diverse set of validation routes. Setting up the relevant process modules requires investment in entirely new capabilities in processing and measurement tools. These modules are the building blocks of a baseline flow and are subject to continuous improvement to ensure maturation, increase learning speed, and drive towards higher TRLs. A steady baseline flow represents an opportunity for R&D collaboration to help materials and equipment vendors stay at the forefront of innovation.

Lower the barrier to advanced chip design with advanced PDKs

The NanoIC pilot line provides early access to advanced process design kits (PDKs) to enable designers in European academia and industry to explore these discoveries in logic, memory, and interconnect technologies.

These PDKs are comprehensive toolsets that provide designers with predictive models, cell libraries, and system-level integration resources to enable accurate simulation and verification of integrated circuits at advanced technology nodes. The availability of these hands-on kits allows circuit designers to explore upcoming chip architectures, address complex design challenges, and support innovation at the 2nm node and beyond.

Specifically, the NanoIC pilot line offers two complementary PDKs. One is a pathfinding PDK for early design exploration of cutting-edge IC technologies, and the other is a system exploration PDK to pave the way for hardware prototyping and system-level innovation.

These PDKs have been released throughout the project and include multiple versions of the N2 Pathfinding PDK, including releases of the A14 and A7 logic PDKs. While memory PDKs are based on advances in eDRAM and SOT-MRAM, advanced interconnect solutions can be considered through RDL, silicon interposers, and D2W hybrid bonding.

Driving innovation in Europe

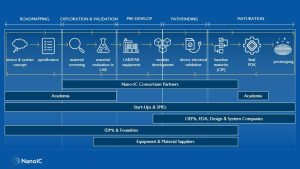

The NanoIC Pilot Line provides flexible access to advanced logic, memory, and interconnect technologies across the semiconductor ecosystem. Companies, research institutes, startups, and universities can collaborate based on their innovation needs.

Manufacturers and foundries of integrated devices can leverage the baseline to explore new modules and performance enhancement options. European and global equipment and materials suppliers are invited to collaborate so that new tools and processes can be tested and refined using the advanced baseline. Additionally, startups, universities, and design firms can access the Pathfinding PDK for early design exploration of future nodes and the System Exploration PDK for hardware prototyping and system-level innovation. Additionally, the NanoIC Pilot Line is dedicated to training the next generation of semiconductor professionals. In partnership with EU Competence Centers, we offer classroom and virtual courses on technologies beyond 2nm, from semiconductor materials to SoC design. Our hands-on internship and study programs provide students with real-world experience, and industry-oriented training prepares our bachelor’s, master’s, and doctoral students for the challenges of the future. The NanoIC Pilot Line is building a skilled workforce to advance Europe’s semiconductor industry through expert courses, technical training and immersive bootcamps.

In summary, the NanoIC pilot line is strategically positioned to bridge the gap between cutting-edge research and commercial applications in the semiconductor industry. The project underlines Europe’s commitment to innovation, competitiveness and sustainable growth in an increasingly digital world. The project aims to strengthen Europe’s leadership in the global semiconductor market by advancing technology and fostering cooperation.

Disclaimer

The acquisition and operation of the NanoIC pilot line is jointly funded by Chips Joint Undertaining and the participating countries Belgium (Flanders), France, Germany, Finland, Ireland and Romania through the European Union’s Digital Europe (101183266) and Horizon Europe programs (101183277). For more information, please visit nanoic-project.eu.

This article is based on comments published in Nature Reviews Electrical Engineering (Volume 1 | December 2024 | 764–765 | 764).

This article will also be published in the quarterly magazine issue 24.

Source link